53 Gbaud PAM4 (100G) Link Demonstrated Using an Analog CDR Technology

Zurich, November 18th, 2019

Tetra Semiconductors Is Partnering with Munich Instruments to Demonstrate a Link at 53 Gbaud PAM4 Using Tetra’s TS1 Chipset.

Tetra Semiconductors Ltd., Zürich, a leading supplier of datacom and test&measurement chipsets and Munich Instruments, Munich, demonstrate the first (to our knowledge) analog CDR based (DSP-less) 53 GBaud electrical Link.

The link setup comprises Munich Instruments’ C-BERT 2810-4 and Tetra-Semiconductors’ TS1 chipset. The C-BERT provides 4 parallel pattern generators and 4 error detectors. Tetra Semiconductors’ TS1 chipset was used to multiplex and demultiplex as well as to encode and decode the PAM4 signals. The TS1 chipset is based on Tetra’s unique NRZ/PAM analog CDR technology (patent pending), which eliminates the need for any DSPs in the link and provides a very low power and low cost solution for electrical and optical links. The TS1 gearbox chips are full-featured, containing retimers, input equalizers (CTLE and DFE), and output pre- and post-cursor emphasis circuits as well as a large set of monitoring features.

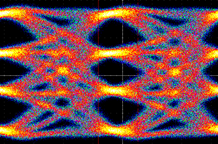

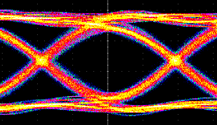

53 Gbaud TSC1ENC output |  53 Gbit/s NRZ TSC1MUX output |

For the link, the 4×26.5 Gbit/s datastreams generated by the C-BERT are muxtiplexed by 2 TSC1MUX ICs into 2 data streams of 53 Gbit/s NRZ. The subsequent PAM4 encoder TSC1ENC generates a 53 Gbaud signal from the two 53 Gbit/s datastreams forming the link transmitter.

For the receiving end of the link, the TSC1DEC retimes and decomposes the PAM4 signal into two 53 Gbit/s NRZ signals using Tetra Semiconductors’ analog PAM4 RF CDR technology. The two 53 Gbit/s NRZ signals are each split into two 26.5 Gbit/s NRZ signals by TSC1DEM’s. All four data streams are fed back into the error detector of the C-BERT.

In testing, the link has been shown to run successfully for more than 24 hours, showcasing robustness and temperture stability. “We are proud to be among the first companies capable of handling the complex PAM4 modulation scheme at very high baud rates using Tetra’s low power and low cost analog CDR Technology.” said Martin Bossard, CEO of Tetra Semiconductors.

Dr. Jörg Wieland added “This is a major milestone in our journey which started three years ago as it demonstrates the full capabilities of Tetra’s PAM4 technology at state-of-the-art speed.”

The TS1 chipset is the base technology for all upcoming PAM4 SR8/LR4/LR8 chipsets released by Tetra Semiconductors.

Following list summarizes all Tetra Semiconductors’ ICs used:

| TSC1ENC | 14/28/56 GBaud PAM4 Encoder | The TSC1ENC converts two NRZ signal inputs into a single PAM4 signal of the same baud rate at the output. The chip can operate at input bit rates of 56 Gbit/s, 28 Gbit/s, and 14 Gbit/s. |

| TSC1DEC | 14/28/56 GBaud PAM4 Decoder | The TSC1DEC converts a PAM4 signal input into two NRZ signals of the same bit rate at the output. The chip can operate at input baud rates of 56 Gbaud, 28 Gbaud, and 14 Gbaud. |

| TSC1MUX | 14/28/56 Gbit NRZ Multiplexer | The TSC1MUX converts two NRZ signal inputs into one NRZ signal of double the bit rate at the output. The chip can operate at input bit rates of 28 Gbit/s and 14 Gbit/s. |

| TSC1DEM | 14/28/56 Gbit NRZ Demux | The TSC1DEM converts a NRZ signal input into two NRZ signals of half the bit rate at the output. The chip can operate at input bit rates of 56 Gbit/s, 28 Gbit/s, and 14 Gbit/s. |

For further information please visit www.tetra-semi.com or get in touch with us via email: info@tetra-semi.com.