Tetra Semiconductors’ Sample of the New PAM4 200/400G Ethernet Transceiver Chipset Now Available

Zurich, March 5, 2020

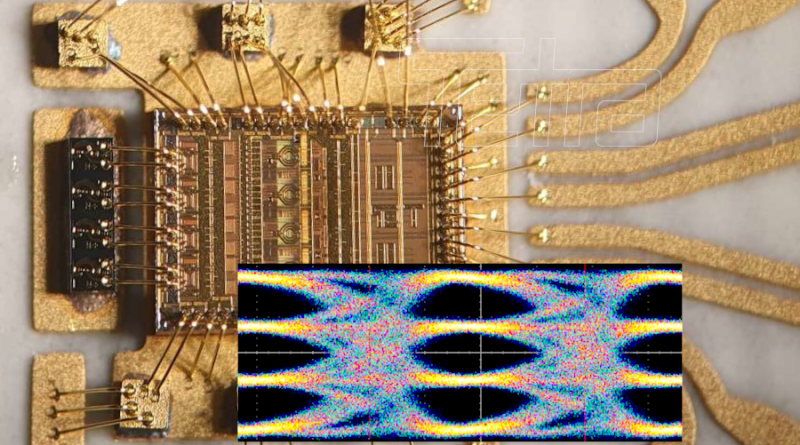

Tetra Semiconductors Ltd., Zurich, Switzerland announces their new TS2 Transceiver Chipset for 200G/400G Ethernet SR/LR applications is now available. The chipset combines outstanding performance with minimal power consumption and offers the cost-effectiveness required to build competitive 200G/400G optical modules.

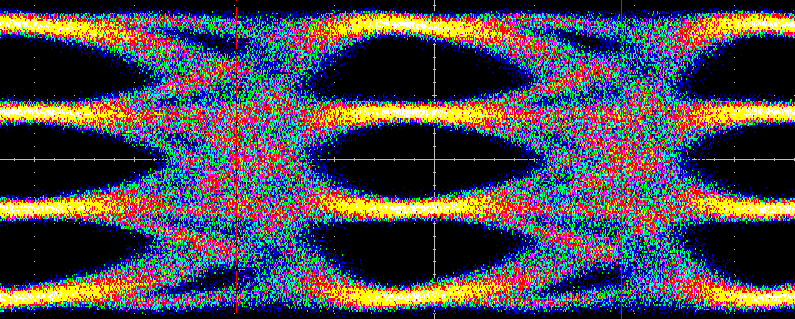

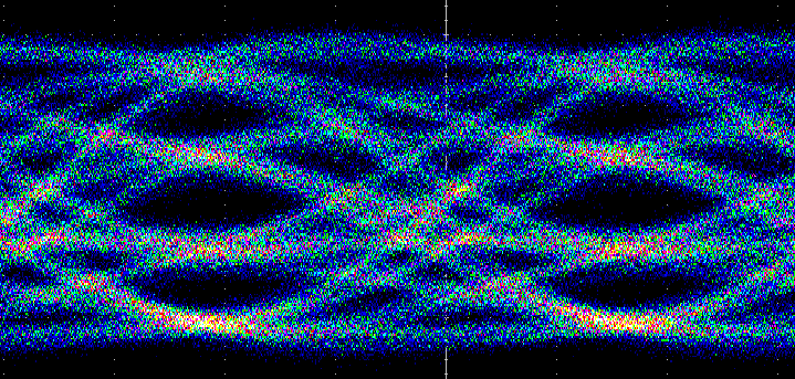

Tetra Semiconductors’ transeiver chipset includes 4 Channel PAM4 VCSEL Drivers and 4 Channel PAM4 TIAs as well as 4 Channel PAM4 CDR chips, all running in the range of 23-29 Gbaud suitable for 200G and 400G Ethernet/Infiniband and other proprietary solutions. The transceiver chipset enables QSFP-DD/OSFP module designs with best in class power consumption of <7 W for the complete 400G module. The TS2 chips are based on Tetra’s 3rd generation patented analog CDR allowing for very low power due an extremely simple, scalable PAM4 decoding scheme. Tetra was the first to show a DSP-free 56 Gbaud link using their unique PAM4 CDR technology! (https://www.tetra-semi.com/news/53-gbaud-pam4-100g-link-demonstrated-using-an-analog-cdr-technology/).

Circuit optimization and newly designed optical front-ends allow for the integration of the CDR with the optical front-ends onto a single chip resulting in the best possible power and a compact size. All chips include adaptive equalization including CTLE and DFE as well as pre- and post-cursor equalization to recover/preshape for the losses of the in/output signals.

Features included in the chips are:

TST2PAM:

- 4 Channel PAM4 CDR with integrated VCSEL Driver

- 50 Ohm inputs with adaptive CTLE and DFE equalization

- PAM4 VCSEL Driver with individual eye adjustment to overcome possible VCSEL nonlinearities

- Power consumption of 390 mW/Channel (10 mA Average Current; 10 mA Modulation Current)

- Size: 2mm x 1.5mm

TSR2PAM:

- 4 Channel PAM4 CDR with integrated TIA

- PAM4 TIA with gain controlled linear amplifier that includes adaptive CTLE and DFE equalization

- 50 Ohm outputs with pre- and postcursor equalization

- Power consumption of 430 mW/Channel (300 mVpp output swing)

- Size: 2mm x 1.5mm

TSC2PAM:

- 4 Channel PAM4 CDR with high output swing of up to 1.4Vpp, enough to drive silicon photonics modulators

- 50 Ohm inputs with adaptive CTLE and DFE equalization

- 50 Ohm outputs with pre- and postcursor equalization

- Power consumption of 410 mW/Channel (@ 1 Vpp output swing)

- Size: 1.8mm x 1.5mm

Samples of all three chips are available now.

For further information please visit www.tetra-semi.com or contact us at: info@tetra-semi.com.